控制管理系统及照明光源的发展状况,针对当前隧道照明控制系统存在的问题。设计了

。本系统充分的利用电子技术和通信技术,实现对隧道灯具的有效控制与管理。本文分析比较了当前各种隧道照明光源的特点,确定选择

作为隧道灯具,并根据车流jI{=和洞外亮度的变化对LED隧道灯进行无级控制,使隧道内各区段照度平滑过渡,以符合人眼的适应曲线,并利用

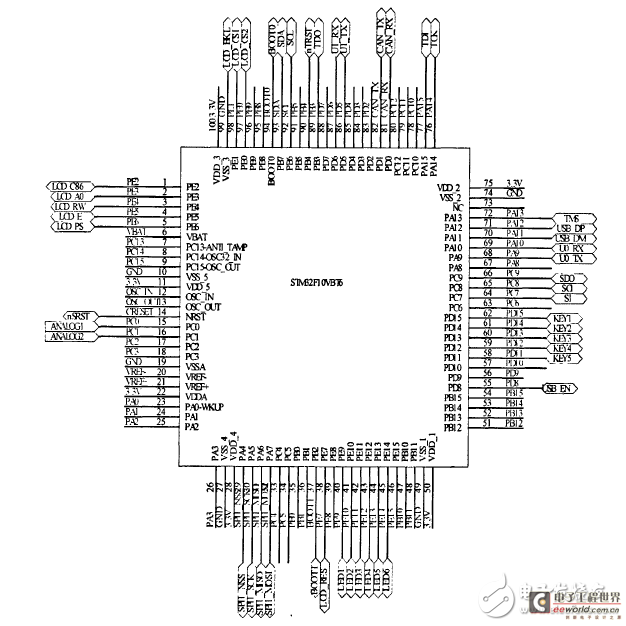

硬件设计的任务是根据系统的设计的基本要求,在所选定的微处理器芯片和其他元器件的基础上,设计出系统的电路原理图,还包括结构设计、印制板设计等。在设计完成后做试验,以便对其不合理的部分进行修正,并最终确定硬件设计的具体方案和完成印制电路板。中心控制器电路最重要的包含以下几个部分:(1) 电路核心部分:ARM微处理器、复位电路、晶振电路和电源电路。(2)JTAG电路:实现程序下载与在线) 外围电路:CAN总线通信电路、USB接口、存储电路、LCD液晶显示、键盘电路、串行通讯电路。

中心控制器的微处理器引脚图如图3.2所示,它最重要的包含芯片中所使用的各个接口的网络标号及与外围电路的连接方式。

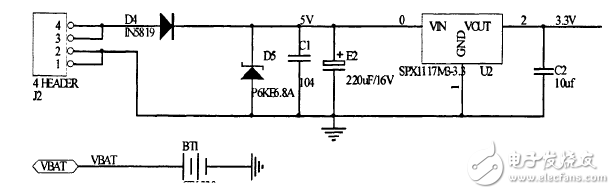

STM32的工作电压为2.0V.3.6V,通过内置的电压调节器提供所需的1.8V电源。当主电源掉电后,通过VBAT脚为实时时钟(RTC)和备份寄存器提供电源。5v电源通过J2端口接入电路,并通过SPXlll7M3.3.3将电源稳压至3.3V。VDDA与VSSA必须分别连到VDD与VSS,这是为降低噪声和出错几率。SPXI 1l 7M3.3.3输出电流可达800mA,输出电压的精度在正负百分之一之间,具有电流限制和热保护功能。P6KE6.8A为瞬态抑制二极管,它有效地保护电子线路中的精密元器件,免受各种浪涌脉冲的损坏。电源不仅是核心电路的供电电源,而且还要负责给其他外围电路供电,电源和地之间的电容是用来去耦的,它提高了系统的抗干扰性。

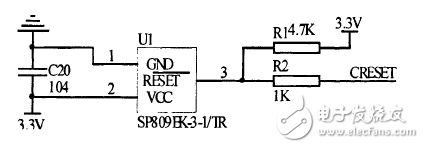

STM32F103VBT6支持三种复位形式,分别为系统复位、上电复位和备份区域复位。除了时钟控制寄存器RCC CSR寄存器中的复位标志位和备份区域中的寄存器以外,系统复位将复位所有寄存器至它们的复位状态。外部复位电路如图3.4所示。

SP809EK.3.1/TR为单功能复位监控器件。当系统上电或电源电压跌落至阈值电压,SP809的复位信号RESET就会产生140ms的复位脉冲,保证系统可靠有效的复位。它的输出典型值为上拉低电平,因此要在RESET--与“电源电压之间加一个上拉电阻Rl。此电路为外部复位,CRESET连接至lJSTM32F103VBT6的NRST引脚上.低电平有效。

语音识别被认定是未来物联网领域的基础需求之一,甚至将会无处不在,详情》》》

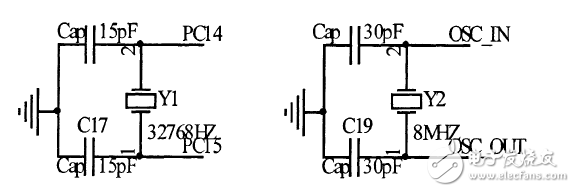

在STM32中,三种不同的时钟源可被用来驱动系统时钟(SYSCLK):HSI振荡器时钟、HSE振荡器时钟和PLL时钟。高速外部时钟信号(HSE)由以下两种时钟源产生:HSE外部晶体/陶瓷谐振器和HSE用户外部时钟。HSI时钟信号由内部8MHz的RC振荡器产生,可直接作为系统时钟或在2分频之后作为PLL输入。LSE(低速外部时钟信号)晶体是一个32.768KHz的低速外部晶体或陶瓷谐振器。晶振电路如图3.5所示。

左图为LSE时钟,它采用32.768kHz夕b部晶振,为实时时钟(RTC)提供一个低功耗且精确的时钟源。LSE晶体通过在备份域控制寄存器里的LSEON位启动和关闭。右图为HSE时钟,采用8MHz夕b部晶振,负载电容值根据所选晶振选取,为系统提供更为精确的主时钟。为减少时钟输出的失真和缩短启动稳定时间,晶体和负载电容必须尽可能地靠近振荡器引脚。

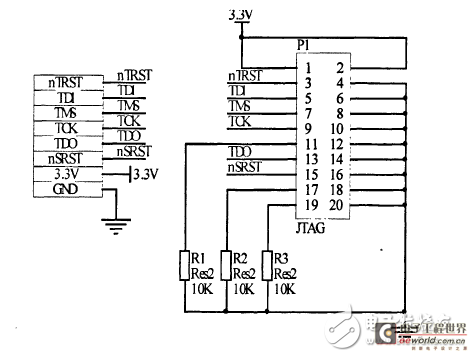

JTAG是一种国际标准测试协议(IEEEl 149.1兼容),大多数都用在芯片内部测试。现在多数高级器件都支持JTAG协议。JTAG g路如图3.6所示,这里使用的是20针JTAG接口。各引脚名称及功能如下:1脚为VTrefH标板参考电压,接电源;2脚为VCC电源;3脚为nTRST狈0试系统复位信号;5脚为TDI钡IJ试数据串行输入;7脚为TMS、狈IJ试模式选择;9脚为TCK测试时钟:1 1脚为RTCK测试时钟返回信号,不使用时可以直接接地;1 3脚为TDO测试数据串行输出;15脚为nSRSTg[标系统复位信号,与目标板上的系统复位信号(NRST)相连,;4、6、8、10、12、14、16、18、20脚为GND接地;17、19脚未定义。

R1、R2、R3均为下拉电阻,令系统复位以后,STM321为部JTAG接口使能,JTAG就可仿真调试。ARM通过JTAG电路与主机的并口连接,先下载程序到FLASHI勾再在器件内通过软件控制程序的运行,由JTAG接口读取片内信息供调试使用的办法来进行开发。这种方式不需要仿真器和编程器,快速缩短了开发周期,降低了开发成本。

STM32具有先进的内核结构和优秀的功耗控制,并且具有性能出众的片上外设。其USB接口可达12Mbit/s,USART接口高达4.5Mbit/s。它采用基于ARMv7.M体系结构的32位标准处理器Cortex.M3,是专门为微控制管理系统、工业控制管理系统和无线网络系统等功耗和成本敏感的嵌入式应用领域实现高系统性能设计的。

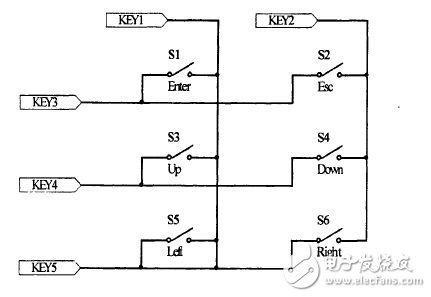

本部分采用简单的矩阵式键盘设计,电路如图3.7所示,这样不仅减少I/O UI的占用,而且便于以后的扩展。这里采用行扫描法,进行按键识别。首先,判断键盘中有无键按下:将全部行线)置低,然后检验测试列线)的状态。

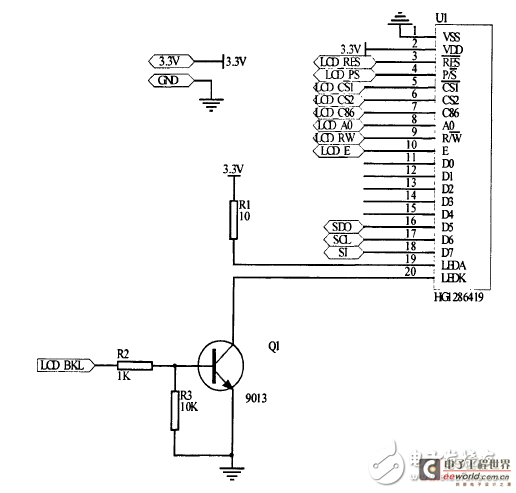

本系统中的LCD显示模块大多数都用在中心控制器脱离上位机独立工作时的命令发送与处理。选用清达光电技术有限公司的HGl286419-SYH.LSV型号的图形点阵液晶显示模组,它支持串行和并行两种接口,点阵数为128“64,内置芯片为EPL651 32,可方便的与各种微处理器相连接。

LCD模块的接口电路如图3.8所示。其工作电压为3.3V,与STM32SE作电压相同,因此能直接用电源电路的输出电压,无需额外电源电路设计。它的显示像素为蓝黑色,显示背景为黄绿色。采用模拟串行通信与ARM芯片连接,连接引脚为SDO(串行数据输出)、SCL(串行时钟)、SI(串行数据输入)分别接蛩jSTM32上的PC9、PC8、PC7引脚上。LCD RES为复位信号,低电平有效。LCD PS用来选择数据传输接口,高电平为并行接口,低电平串行接口。LCD CSl和LCD CS2为片选信号。LCD C86用来选择时序,高电平为6800时序,低电平为8080日-j序。LCD A0用来发送数据还是命令,高电平为数据,低电平为命令。LCD RW用来选择读写信号,当为6800时序时,高电平为读信号,低电平为写信号,当为8080Bt序时为写信号。LCD E为6800时序的使能信号或8080时序的读信号。LEDA脚和LEDK脚为LED背光源输入,LEDA接3.3V,LEDK应接地。此处由LCD BKL控制晶体管导通.然后控带rJLEDK的电平。

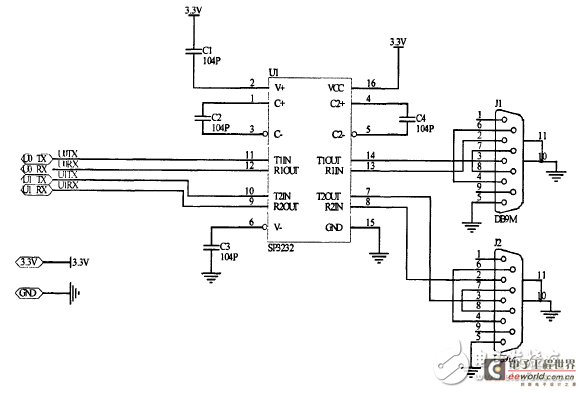

本系统采用的是标准的DB.9接口,电路如图3.9所示。由于RS.232.C标准采用负逻辑方式,与STM32F103VBT6的LVTTL电路所定义的高低电平信号完全不同,所以要用SP3232进行RS232电平转换,SP3232的工作电压为+3.05.OV,将EIA/TIA.232电平转换为TTl或CMOS电平。这里有两路串行通信接口,U0和U1。

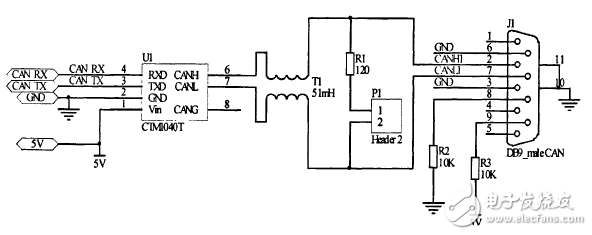

CAN总线所示。由于系统中心控制器要与节点控制器进行通信,因此硬件部分包括CAN通信模块设计,采用CTMl040T是一款带隔离的高速CAN收发器芯片,该芯片内部集成了所有必需的CAN隔离及CAN收、发器件。该芯片的基本功能是将CAN控制器的逻辑电平转换为CAN总线的差分电平并且具有DC2500V的隔离功能及ESD保护作用。T1为高频扼流圈,因为隧道里环境复杂,高频扼流圈可以滤除高频干扰,使电路稳定。

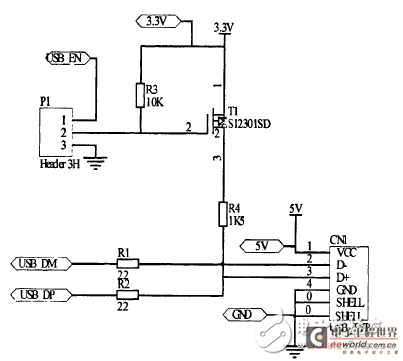

USB且P串行通用总线针插头作为标准插头,其电路设计如图3.1l所示。USB的D+与D.是差分输入线V电压。而电源与地线mA。USBEN用于控制是否使能USB通信功能,控制D+和D.的电平。

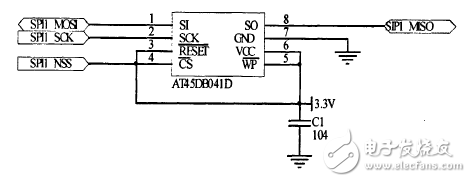

由于隧道照明需要存储操作记录,包括调光值、操作时间、操作组别等信息,因此使用AT45DB041D存储数据,电路如图3.12所示。它通过SPI总线与ARM处理器通信,在需要的时候能通过上位机发送命令读取历史记录,并且历史记录存储会自动定期清除。CS为芯片选择引脚,CS脚由高到低的电平转换时开始对芯片做相关操作,反之,由低到高时结束操作。SCK是串行时钟,SO是串行数据输出,SI是串行数据输入。WP是写保护,WP引脚已经内置上拉,在不使用时,将它接到高电平上。RESET是复位,只要RESET恢复到低电平即可对芯片做正常操作,芯片内部已经内置了上电复位电路,不使用此引脚时将它接到高电平上。

系统最重要的包含上位机监控中心、检测设备、中心控制器、节点控制器和LED驱动电源。通过检测设备采集数据,然后传递给上位机监控中心,上位机进行数据处理之后,向中心控制器发送命令,中心控制器以广播形式向节点控制器发送命令,通过调节LED驱动电源的输入电压控制LED灯的亮度。中心控制器与节点控制器采用CAN总线通信,中心控制器与上位机采用串口通信。

制定了中心控制器、节点控制器与上位机之间的通信协议,并对中心控制器和节点控制器进行了硬件电路设计,最重要的包含微处理器的选型、通信模块设计、DA转换电路设计、液晶显示设计、数据存储模块设计、放大电路设计,并给出了部分电路的详细原理图。